### Automotive 3-Phase MOSFET Driver

### **Features and Benefits**

- High current 3-phase gate drive for N-channel MOSFETs

- SPI compatible serial control

- Cross-conduction protection

- Programmable dead time

- 5.5 to 50 V supply voltage range

- TTL inputs compatible with 3.3 V and 5 V logic

- Extensive diagnostics output

- · Low current sleep mode

### **Applications**

- Electronic power steering (EPS, EHPS, EAS)

- · Hydraulic pumps

- · Gearbox actuator

# Package: 28-pin TSSOP with Exposed Thermal Pad (suffix LP)

Not to scale

### **Description**

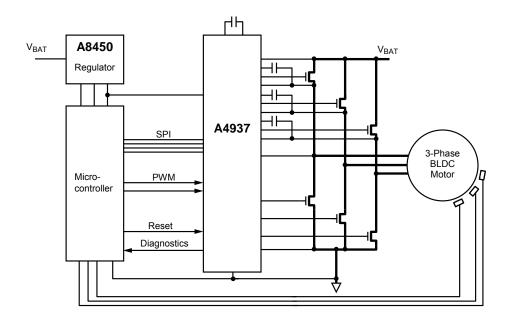

The A4937 is a 3-phase controller for use with N-channel external power MOSFETs and is specifically designed for automotive applications.

A unique charge pump regulator provides full (>10 V) gate drive for battery voltages down to 7 V and allows the A4937 to operate with a reduced gate drive, down to 5.5 V.

A bootstrap capacitor is used to provide the above battery supply voltage required for N-channel MOSFETs.

Full control over all six power MOSFETs in the 3-phase bridge is provided, through an SPI compatible serial interface, allowing motors to be driven with block or overlap commutation. Power output can be regulated by one or both of the PWM inputs. The power MOSFETs are protected from shoot-through by integrated crossover control and programmable dead time.

Integrated diagnostics provide indication of undervoltage, overtemperature, and power bridge faults, and can be configured to protect the power MOSFETs under most short circuit conditions. Detailed diagnostics are available as a serial data word.

The A4937 is supplied in a 28-pin TSSOP power package with with exposed pad for enhanced thermal dissipation (package type LP). This package is lead (Pb) free, with 100% matte-tin leadframe plating.

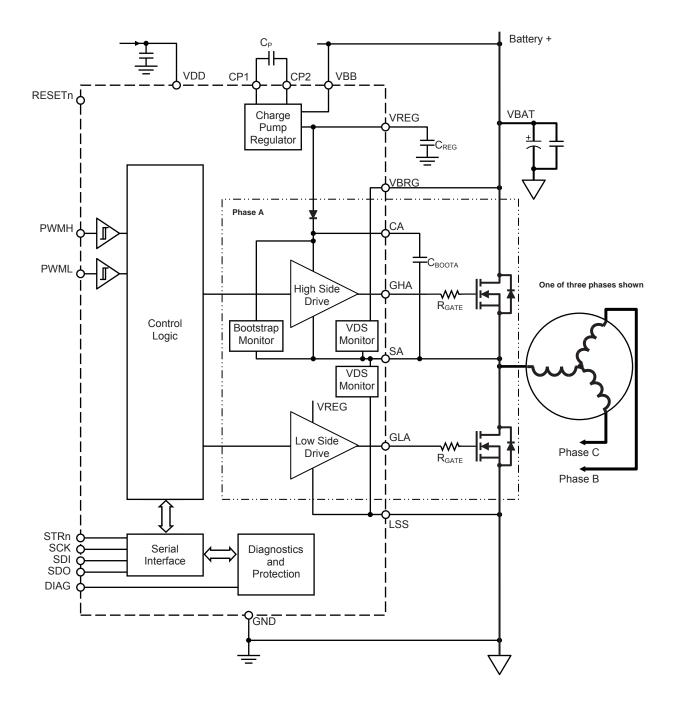

### **Functional Block Diagram**

## Automotive 3-Phase MOSFET Driver

### **Selection Guide**

| Part Number    | Packing*                    | Package                                                               |  |

|----------------|-----------------------------|-----------------------------------------------------------------------|--|

| A4937KLPTR-A-T | 4000 pieces per 13-in. reel | 4.4 mm × 9.7 mm, 1.2 mm maximum height TSSOP with exposed thermal pad |  |

### **Absolute Maximum Ratings\***

| Characteristic                                   | Symbol               | Notes                                                                                                                     | Rating                                           | Unit |

|--------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------|

| Load Supply Voltage                              | V <sub>BB</sub>      |                                                                                                                           | -0.3 to 50                                       | V    |

| Logic Supply Voltage                             | V <sub>DD</sub>      |                                                                                                                           | -0.3 to 6                                        | V    |

| Terminal VREG                                    | V <sub>REG</sub>     |                                                                                                                           | -0.3 to 16                                       | V    |

| Terminal CP1                                     | V <sub>CP1</sub>     |                                                                                                                           | -0.3 to 16                                       | V    |

| Terminal CP2                                     | V <sub>CP2</sub>     |                                                                                                                           | $V_{CP1} - 0.3 \text{ to} $<br>$V_{REG} + 0.3$   | V    |

| Lagia Innuta                                     | VI                   | STRn, SCK, SDI, PWMH, PWML                                                                                                | -0.3 to 6                                        | V    |

| Ferminal DIAG Ferminal VBRG Ferminals CA, CB, CC | VI                   | RESETn; can be pulled to $V_{BB}$ with >22 k $\Omega$                                                                     | -0.3 to 6                                        | V    |

| Logic Outputs                                    | Vo                   | SDO                                                                                                                       | -0.3 to V <sub>DD</sub> + 0.3                    | V    |

| Terminal DIAG                                    | V <sub>DIAG</sub>    |                                                                                                                           | -0.3 to V <sub>DD</sub> + 0.3                    | V    |

| Terminal VBRG                                    | $V_{BRG}$            |                                                                                                                           | -5 to 55                                         | V    |

| Terminals CA, CB, CC                             | V <sub>Cx</sub>      |                                                                                                                           | -0.3 to V <sub>REG</sub> +50                     | V    |

| Terminals GHA, GHB, GHC                          | V <sub>GHx</sub>     |                                                                                                                           | V <sub>Cx</sub> – 16 to<br>V <sub>Cx</sub> + 0.3 | V    |

| Terminals SA, SB, SC                             | V <sub>Sx</sub>      |                                                                                                                           | $V_{Cx} - 16 \text{ to} $<br>$V_{Cx} + 0.3$      | V    |

| Terminals GLA, GLB, GLC                          | V <sub>GLx</sub>     |                                                                                                                           | V <sub>REG</sub> – 16 to 18                      | V    |

| Terminal LSS                                     | V <sub>LSS</sub>     |                                                                                                                           | V <sub>REG</sub> – 16 to 18                      | V    |

| Ambient Operating Temperature Range              | T <sub>A</sub>       | Limited by power dissipation                                                                                              | -40 to 150                                       | °C   |

| Maximum Continuous Junction<br>Temperature       | T <sub>J</sub> (max) |                                                                                                                           | 150                                              | °C   |

| Transient Junction Temperature                   | T <sub>tJ</sub>      | Overtemperature event not exceeding 10s, lifetime duration not exceeding 10 hours, guaranteed by design characterization. | 175                                              | °C   |

| Storage Temperature Range                        | T <sub>stg</sub>     |                                                                                                                           | -55 to 150                                       | °C   |

<sup>\*</sup>With respect to GND. Ratings apply when no other circuit operating constraints are present.

#### Thermal Characteristics may require derating at maximum conditions

| Characteristic                               | Symbol         | Test Conditions*                                               | Value | Unit |

|----------------------------------------------|----------------|----------------------------------------------------------------|-------|------|

| Package Thermal Resistance (Junction         | D              | On 4-layer PCB based on JEDEC standard                         | 28    | °C/W |

| to Ambient)                                  |                | 2-layer PCB with 3.8 in. <sup>2</sup> of copper area each side | 32    | °C/W |

| Package Thermal Resistance (Junction to Pad) | $R_{	heta JP}$ |                                                                | 2     | °C/W |

<sup>\*</sup>Additional thermal information available on the Allegro website.

<sup>\*</sup>Contact Allegro<sup>TM</sup> for additional packing options.

### **Functional Block Diagram**